As VLSI chips grow increasingly complex, packing billions of transistors into a few nanometers, ensuring that they function exactly as intended before fabrication is more critical than ever. That’s where Functional Verification comes in—a domain that now accounts for over 60–70% of total VLSI design effort and cost.

In this blog, we explore why functional verification is crucial in VLSI design, the different techniques used, the tools involved, and how engineers can build successful careers in this high-demand domain.

What is Functional Verification in VLSI?

Functional Verification is the process of checking whether a chip design performs its intended functions correctly—before it goes to silicon.

It involves:

- Simulating RTL code (Verilog/SystemVerilog)

- Writing testbenches to apply input stimuli and observe outputs

- Ensuring functionality matches the specification

- Catching bugs in logic, sequencing, interfaces, protocols, and data paths

- Functional verification is done throughout the design lifecycle—from early module-level checks to full-chip integration and system-level testing.

Why Is Functional Verification So Important?

1. Chips Are Costly to Fabricate

Once a chip is taped out and fabricated, any bug is irreversible. Fixing it requires re-spins, costing millions of dollars and months of delay. That’s why verification must catch all logic issues upfront.

2. Logic Bugs Are Common & Subtle

Even the best RTL designers can introduce bugs due to:

- Wrong FSM transitions

- Incorrect data routing

- Missed handshake protocols

- Edge cases not handled

Functional verification ensures these logic flaws are caught early—before they reach synthesis or layout.

3. Chip Complexity Is Increasing

Modern SoCs involve:

- Multi-million gate counts

- Multiple clock domains

- High-speed interfaces (PCIe, USB, AXI)

- Multiple IP blocks and processors

Manual testing is no longer sufficient. You need automated, scalable verification strategies like constraint-driven verification and UVM.

4. Directly Impacts Time-to-Market

A bug in post-silicon validation can delay product launch by months. Robust functional verification ensures first-silicon success, giving companies a major competitive edge.

Types of Functional Verification Techniques

| Technique | Description |

|---|---|

| Simulation-Based Verification | Most widely used; applies input vectors to RTL and checks output against expected behavior. |

| Formal Verification | Uses mathematical proof to validate properties (e.g., assertions). |

| Emulation | Runs RTL on hardware accelerators for faster testing of large SoCs. |

| FPGA Prototyping | Maps design onto FPGA to validate in near real-time. |

| Coverage-Driven Verification (CDV) | Measures how much of the design has been tested (code, functional, assertion coverage). |

Most companies use a combination of simulation + UVM + coverage metrics for robust chip validation.

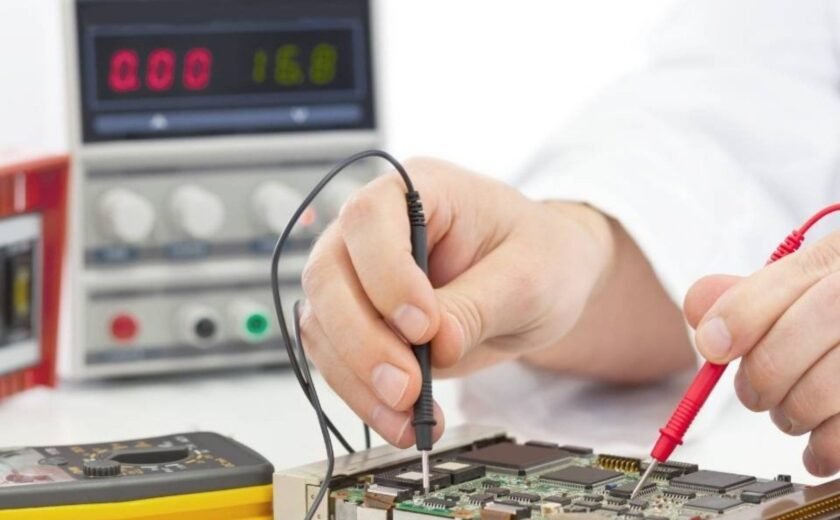

Tools Used in Functional Verification

| Tool | Function |

|---|---|

| ModelSim / QuestaSim | Simulation and waveform debugging |

| VCS (Synopsys) | High-performance simulation |

| Incisive / Xcelium (Cadence) | Industry-grade functional verification |

| SystemVerilog | HDL + testbench + assertions |

| UVM (Universal Verification Methodology) | Structured, reusable testbench framework |

| Verdi / DVE | Waveform viewing and debugging |

At MOSart Labs, students get real-world exposure to these tools as part of project-based learning.

Career Opportunities in Functional Verification

Functional Verification is one of the highest-paying and fastest-growing VLSI domains, with roles such as:

- Verification Engineer

- UVM Testbench Developer

- Design & Verification Engineer

- ASIC Verification Engineer

- SoC Validation Specialist

Average starting salaries in India for trained verification engineers range between ₹6–12 LPA, with rapid career growth.

How MOSart Labs Prepares You for Verification Roles

Our IIT Bhubaneswar-certified VLSI PG Diploma gives you a complete foundation in RTL + Functional Verification, with emphasis on:

- SystemVerilog syntax and best practices

- Building layered UVM testbenches

- Writing assertions and coverage models

- Running simulations and analyzing waveforms

- Debugging real RTL design issues

- Hands-on with VCS, QuestaSim, and ModelSim

- Live projects based on industrial chip specs

We ensure you’re job-ready for roles in Tier 1 companies by combining tool skills, theory, and placement support.

Final Thoughts

In the world of VLSI, you don’t get a second chance after tape-out. That’s why functional verification is not just important—it’s mission-critical.

Whether you want to build a career in RTL, DFT, or SoC design, understanding and mastering verification principles is non-negotiable. It’s where engineering logic meets real-world reliability.

With the right training, tools, and mentorship, you can become a verification expert who ensures silicon success—every time.

At MOSart Labs, we’re here to help you build that expertise.